Introduction

I couldn’t resist the temptation to try and build quickly the SLCF design proposed here. It was question of building a simple PCB for the tail CCS and the top MOSFET follower. Wiring it then point-to-point could be done in a matter of minutes and a “rat nest” was built fast enough to enjoy this learning experience.

The usual challenges we face when breadboarding circuits

One of the challenges we face when building a cathode follower with a high-gain / transconductance valve is that it can easily oscillate widely into VHF. So we then are a bit more precocious when building the test jig and “try” to have short connections (something which I didn’t do), add some ferrite beads to anode, grid and screen. Also some grid/screen stopper resistors (e.g. 300Ω) are always very useful. If you pay attention to this and check with an oscilloscope with sufficient bandwidth (e.g. 200MHz) you can spot out any nasty oscillation from the valve. I didn’t, thanks to the ferrite beads and stoppers.

The clear challenge of the SLCF is establishing the correct bias point on the top follower due to the high value of the resistor divider and the high-variance we typically get on the VGS(th) of the MOSFETs.

High-value resistors are available on 1% but the variance on the FET defeat the purpose of accurately building the resistor divider.

An alternative approach is to replace the resistor divider by a classic LND150 CCS and a resistor. This adds complexity, of course but makes it easier to implement and adjust on test with a small value trimmer. Here is an example:

In the above circuit, M2 with Rtrim forms the CCS and feeds a small current (500uA) through R8 to develop the voltage required. Rtrim can be a 2k trimmer. I don’t think is worth the extra complexity in my view.

In the above circuit, M2 with Rtrim forms the CCS and feeds a small current (500uA) through R8 to develop the voltage required. Rtrim can be a 2k trimmer. I don’t think is worth the extra complexity in my view.

I built the original circuit as-is and although it was working fine, I couldn’t bias the top FET so output distortion was considerable (i.e. circa 0.01% or higher). This was more evident in higher frequencies. I played around with adding a 1M potentiometer and managed to set the voltage but also destroyed the DN2540 whilst playing with it. Clearly no gate protection diode was added, my fault.

So I changed instead for a sturdy STP3NK60ZFP which I have plenty of. This MOSFET has gate protection diodes and also comes in a handy plastic TO-220 package which makes it safer for my clumsy fingers 🙂

So I proceeded to rebuild the circuit below:

If you don’t have some sort of FFT capability with a soundcard or similar I suggest you don’t try this circuit. Why? Because without looking at the harmonic profile you won’t easily find out if the top FET is biased properly. You can’t place your voltmeter on the gate of the FET. That high-impedance node will go hell when you place the tip of your voltmeter. So despite having a functional circuit, we may have a distorted follower! Your ears might tell you that. Best to have a FFT to see if its working properly or not.

In my case, it didn’t first time round. Distortion was high, however if you dial up the HT voltage you can get the FET to bias but you push out the operating point of the valve. It will work and you will see the THD to drop massively, well below you can expect.

First test

So I dialled up the HT to 220V and the distortion was below 0.003%. Great stuff:

The harmonics are below the 100dB floor. As clean as it gets!

If we look at the response in frequency, and particularly the HF response we can see:

The LF distortion is due to the mains hum I have on the rat nest. The THD stays below 0.003% up until 10-20kHz, nice.

The LF distortion is due to the mains hum I have on the rat nest. The THD stays below 0.003% up until 10-20kHz, nice.

Refining the SLCF stage

What you can do is to replace the divider R7 with a pot and find the sweet spot with the FFT for the HT level you want. I proceeded to reduce HT to 200-210V. The distortion is high (all harmonics well above -40dB) until you reach the bias point and they will fall down to -100dB. Then you disconnect the pot and measure the value. For the FET I used I found 270K to be ok. I replaced it with a film resistor and fired up the circuit again. I could now get 0.0025% for 1Vrms.

Here is the final circuit with actual measurements of my test jig:

The HT was set somewhere between 205 and 210V. It can vary somehow. The 6J52P was biased to 176V/16.2mA in the end. The 1.24V grid bias seems not to draw any grid current.

The HT was set somewhere between 205 and 210V. It can vary somehow. The 6J52P was biased to 176V/16.2mA in the end. The 1.24V grid bias seems not to draw any grid current.

The high impedance nodes are prone to pick up hum so building this circuit for proper use will require some attention to the wiring.

I still need to do further tests including the 7KΩ load and higher voltage levels.

So far, it has been a very insightful experience. We always learn something whilst experimenting with circuits and topologies. It’s very useful to pick up the solder and try it. We will always find something new, for sure.

There is no doubt I will build this circuit properly now. I need to get the power supply ready and tested and then back to the tedious work of the proper mechanical build, which I utterly hate.

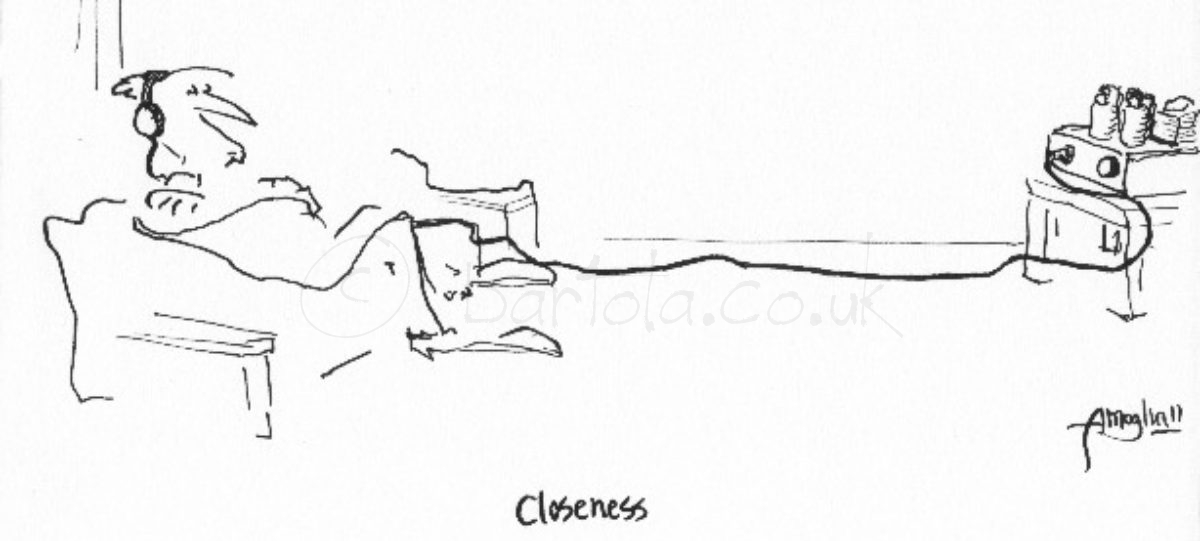

Now, I put on the Wayne Shorter “Adam’s Apple” record on the turntable, time to relax.

Dear Ale,

thanks for this excellent (and educative) description of your progress. I’m following closely as I was aiming for an “easy upgrade” of my 6e6p based Heretical Pre-Amp (Sy, Diyaudio), being exactly such a cathode follower as yours initially.

So, I have to accept to equip myself with an appropriate (Mac based) FFT capability. Hm.

Furthermore: I’m following your RIAA experiments even closer. Why? Cause I had the idea of a tube based MC RIAA to be built based on these little 6c17k’s but without any input transformer. So, I prepared myself by collecting about 50 of these. Being a beginner (in electronics) I did not start anything yet, but am very interested in your findings & reports.

Ah, and congrats to your baby. I remember the #1 had been really very exciting and time was always an issue. All the best for you & your family,

Ulrich

Thank you Ulrich for your comments!

The SLCF is not easy to get up and running and as said in the post, without the proper gear is hard to check if its working fine. I’d not advise to build your testing equipment around a mac. Being a mac user, I’d suggest you look into a cheap Win laptop to avoid any headaches with the limited software availability or the use of a hypervisor to run Win and potentially not getting the performance you need and ending up with a glitching FFT.

The MC project is progressing slowly. I don’t want to push you away from it, but it may be an advanced project so you may want to start with simpler projects first to get experienced with building valve circuits and then moving into phono.

Fatherhood is exciting but really exhausting!

How did the experiment sound like in the end ? is it worth the extra effort compared to a normal or Loftin-white follower ?